# Non-Contiguous Allocation

### Hosting a party for N people

45

# "Non-Contiguous" Memory Allocation

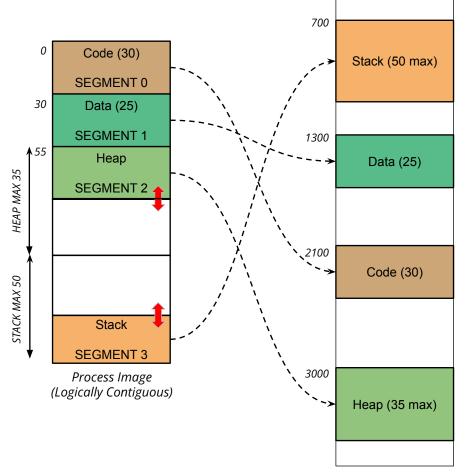

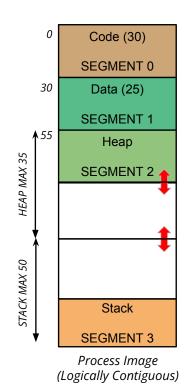

#### • Segmentation

- Split a process memory into several (**non-uniform size**) segments

- Each segment corresponds to a logical unit (typically created by the compiler)

- Code [section/segment]

- Read-only data [section/segment] and R/W data [section/segment]

- Stack [section/segment]

- Heap [section/segment]

- Global data, uninitialized data, ...

- Each segment itself is **contiguous**, but the segments themselves may NOT be

- Paging

- Split a process memory into (**uniform size**) non-contiguous pages

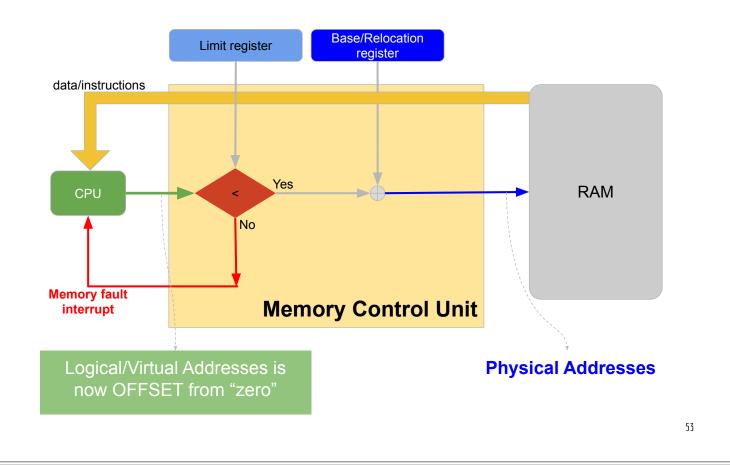

- Can't use just ONE pair of Base Register & Limit Register anymore. Why?

| Segment Table (in RAM) |  |  |  |

|------------------------|--|--|--|

STBR: Segment Table Base Register

| Limit | Base |

|-------|------|

| 30    | 2100 |

| 25    | 1300 |

| 35    | 3000 |

| 50    | 700  |

## Compiler Redesign (to support segmentation)

# Base & Limit Regs (O-based Logical Addr.)

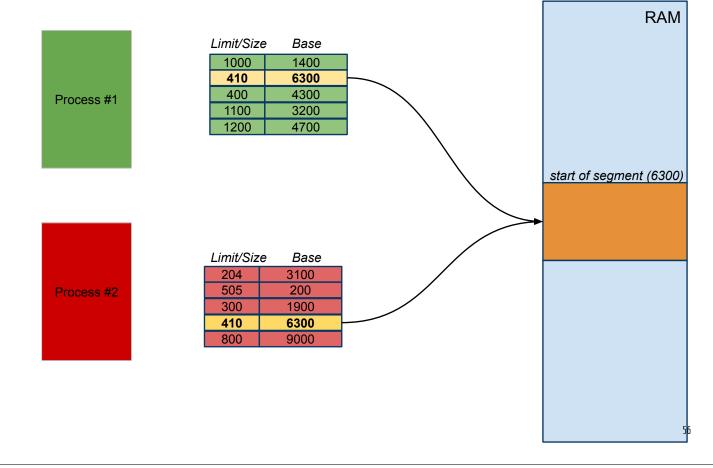

### Shared Segment(s)

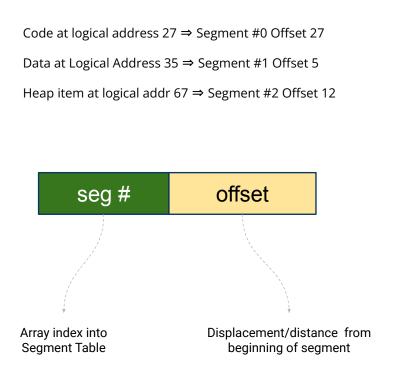

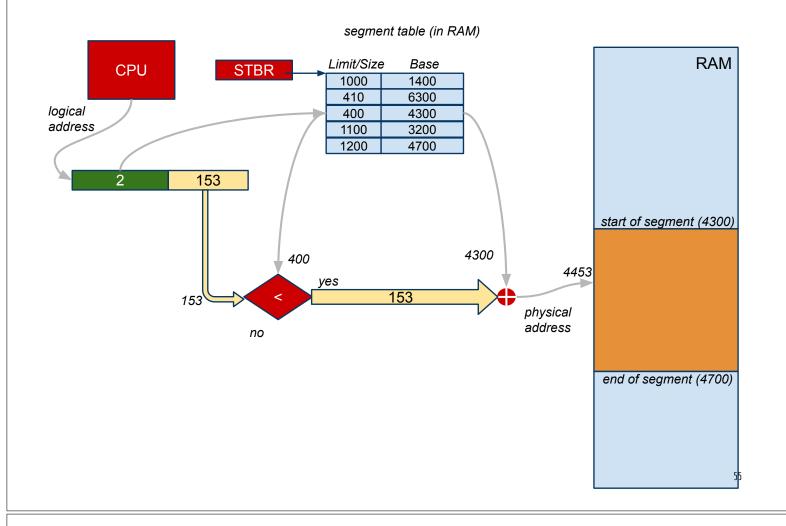

# Segmentation: Memory Address

- Logical address generated the CPU has two parts

- $\circ$   $\;$  Segment number (used for indexing the segment table)

- $\circ \quad \text{Offset within the segment} \\$

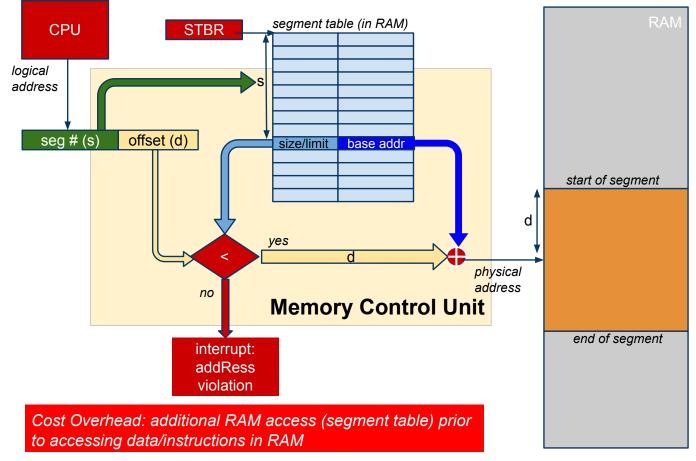

- The OS manages segment tables (**one table per process**). Each segment table entry consists of:

- Size of the segment (mimics the Limit Register)

- Start location of the segment (mimics the Base/Relocation Register)

- The address of the segment table is kept in Segment Table Base Register (STBR)

- STBR must be saved/restored on context-switch

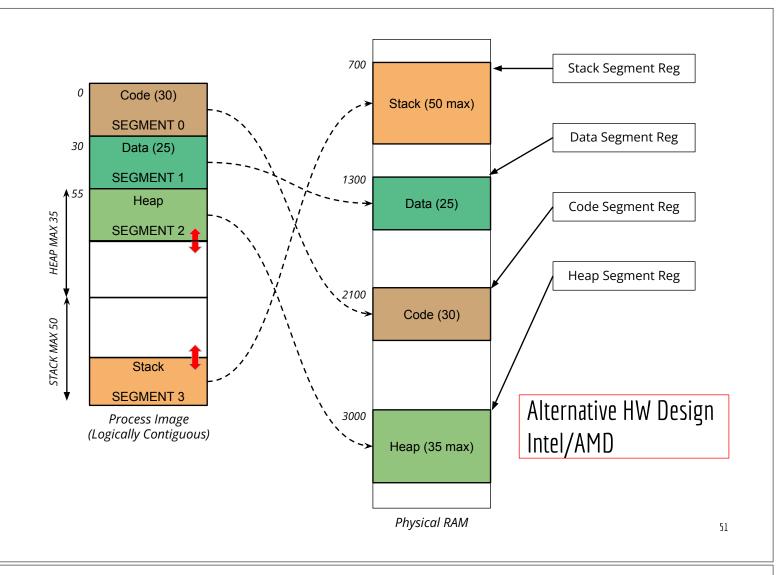

# Case Study: Intel x86 CPUs

57

# Intel x86 (32-bit) Segment Registers

| Register | Description            | Usage                          |

|----------|------------------------|--------------------------------|

| CS       | Code Segment Register  | Access the code                |

| DS       | Data Segment Register  | Access the data                |

| SS       | Stack Segment Register | Access the stack               |

| ES       | Extra Segment Register | String copy/compare operations |

On recent Intel CPUs with 64-bit architecture these registers are not used (set to 0) when the CPU is running in 64-bit mode!

# Quiz: Segmentation & Segment Table