### Warming Up

- Instructor Introduction

- IBM 3090 vector processors supercomputer (precursor to modern GPU)

- Security "plugin": allow at most 4 users at any time to use the vector processors

- Lesson learned:

- Reentrant code at assembly level

- Interrupt mechanism

- <u>Miniature Climbing Robot</u>

- Lesson learned: Build a mini OS: interrupt handler, CPU scheduler, memory manager, I/O

- Brief student Introduction

- Name

- Something unique about you (*to help me learn who you are*)

### Miniature Climbing Robots

### Announcements

- Access to EOS (Lab Thursday and subsequent weeks)

- a. Use SSH Client + VPN required if you access the lab from off-campus

- b. Use Web-based Portal (<u>https://computing.gvsu.edu/</u>)

- Course Web Site at <u>https://dulimarta-teaching.netlify.app</u>

- a. Bb will be used mainly for announcements, collecting assignments, and grading

### Grading/Late Policy

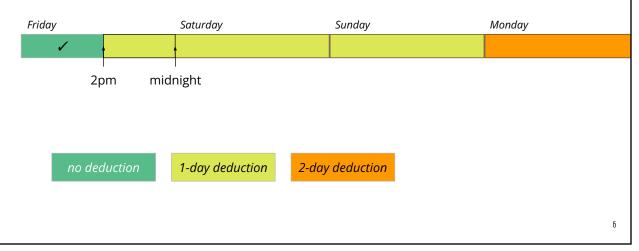

- All assignments are **due at the beginning** of class/lab time

- Each student has a 5-day late quota throughout the semester

- a. University holidays count as 0 day

- b. Sat & Sun are logically the same day

- When your quota goes to zero, late assignments must be turned in no later than 3 days after due date. Apply 15% daily penalty

- No extra assignments will be provided per individual student requests. Use the extra credit opportunities provided in most assignments

Example: Assignment Friday due at 2pm

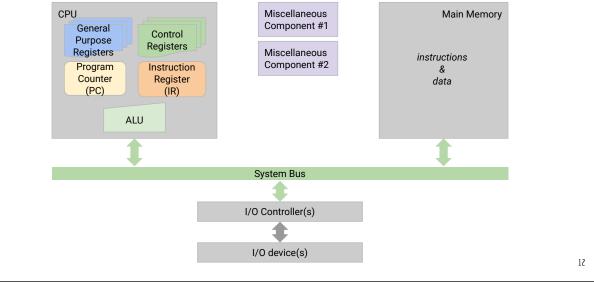

### Basic Computer Hardware Elements

- Processor(s)

- Main Memory

- I/O Controllers & Devices

- System Bus

# Basic Components of Computer Hardware

#### Take away concept:

# *Certain OS functionalities are possible only because of features provided by hardware (CPU)*

## Important Fact/Concept

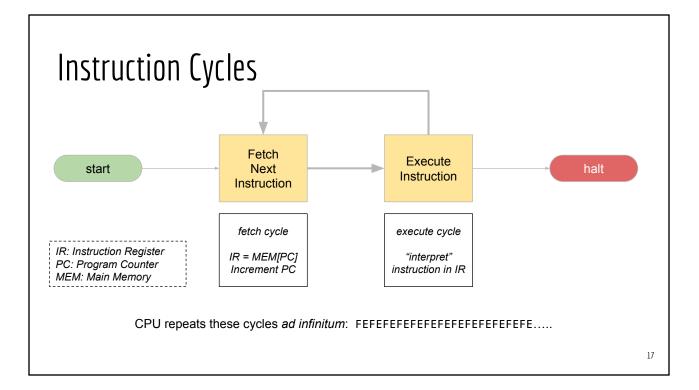

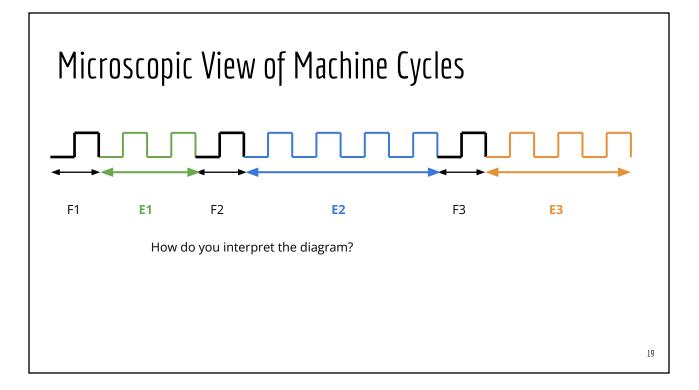

### OS is NOT involved in <u>fetching</u> and <u>executing</u> every assembly instructions on your CPU(s)

18

### Which <u>Hardware</u> Design is Preferred? Why?

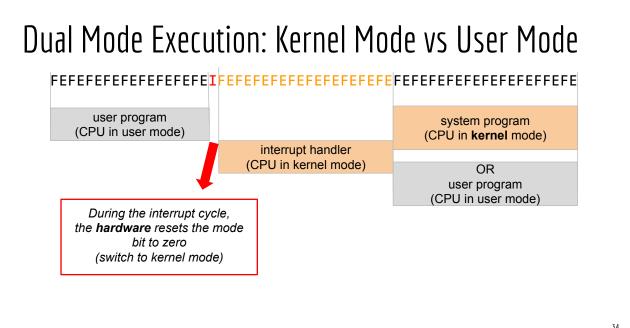

(a) FE FE FE FE FE FE FE FE FE....

(b) FE FE FE FE FE FE FE FE FE FE....

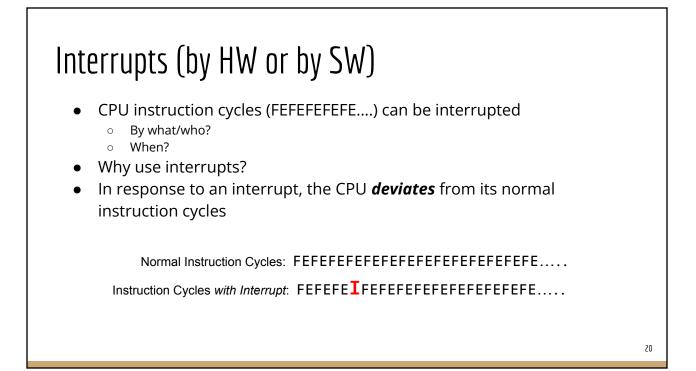

### Interrupts

- Misconception: CPU sends hardware interrupt signal to your program

- Fact:

- a hardware interrupt: signal **asynchronously** received by CPU sent by devices/other units

- a software generated interrupt: **synchronously** triggered by a special assembly instruction, or errors detected during execution of the current assembly instruction

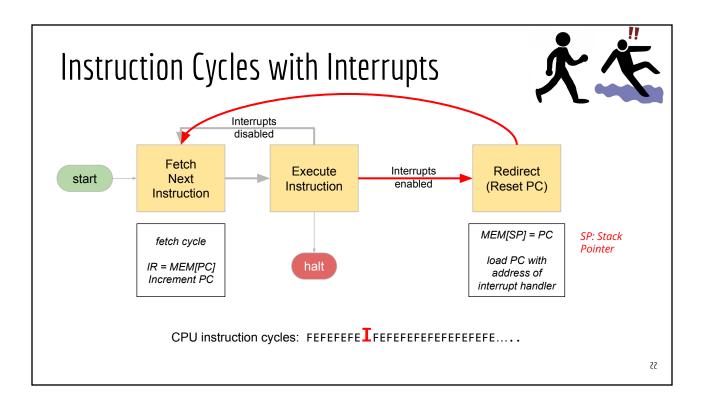

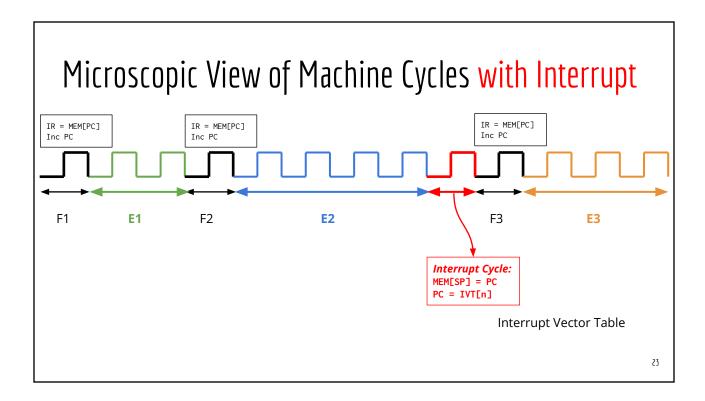

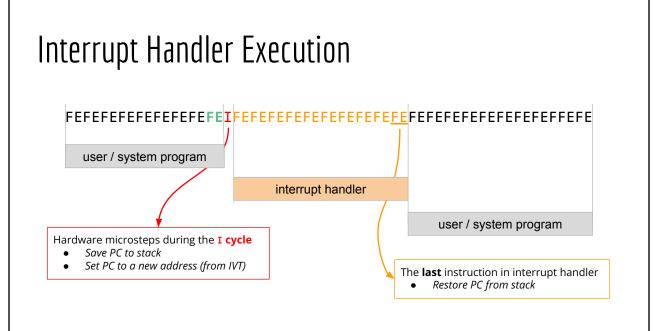

- In response: CPU "immediately" enters its interrupt cycle to service the interrupt request

- Side effect: the current program is interrupted

- Source of interrupts

- (Async) Triggered by other components in your computer

- Real-time clock, keyboard, gyroscope (smartphone), ...

- (Sync) Detected by CPU: Arithmetic errors, unknown instructions, protection error, ....

- (Sync) Requested by **software** (INT or TRAP instruction)

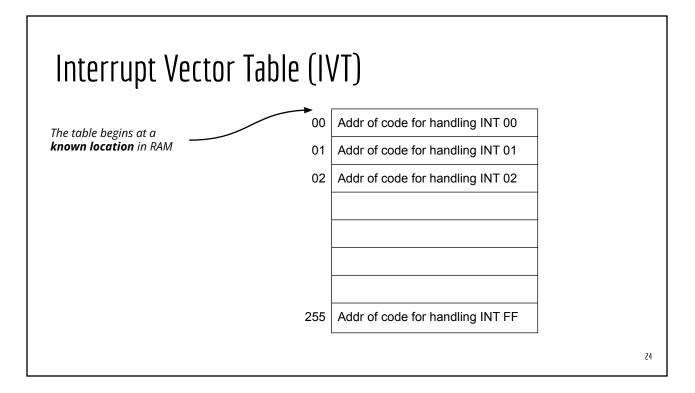

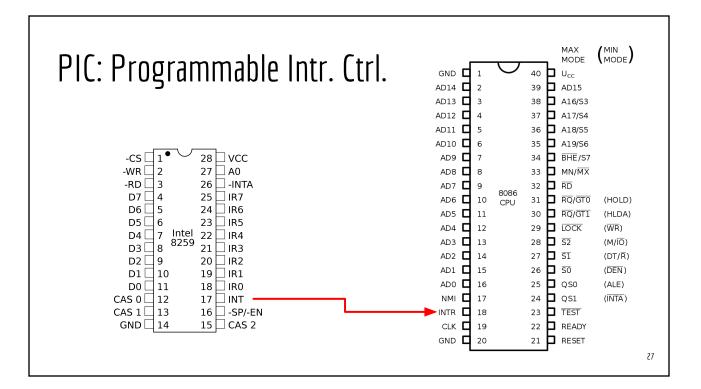

### Interrupt Handler and Interrupt Vector Table

- Interrupt Handler (IH): a small subroutine (part of the OS) that determines the details of the interrupt and performs whatever actions required

- Handling interrupts from multiple of sources:

- Hardware Interrupt requests are numbered: IRQ0, IRQ1, IRQ2, ....

- Assembly instruction to generate **software interrupts** includes a numeric argument

- The addresses of corresponding interrupt handler are stored in a 1D array (Interrupt Vector Table)

- Intel CPUs: Interrupt Descriptor Table and Interrupt Descriptor Table Register

- During its interrupt cycle, the CPU reloads the Program Counter with the right IH address from IVT

How does the OS HW protect itself from malicious programs?

### User Mode vs. Kernel Mode

- Certain CPU instructions are privileged (*should execute only when the CPU is in kernel mode*)

- $\circ$  ~ Examples: **HLT** (to stop the CPU), **CLI** (the disable interrupt), ....

- CPU keeps a mode bit in one of its *control registers*

- mode = 0 (kernel mode): CPU can execute **all the available instruction sets**

- mode = 1 (user mode): CPU can execute **only non-privileged subset** of CPU instructions

- Obviously, setting the mode bit to 0 cannot be done while the CPU is in user mode. Solution?

**Misconception**: User/Kernel mode of the CPU is determined by your login as either a normal user or root/admin user

**Fact**: The CPU mode is unrelated to user access level (admin/root)

- CPU mode is a feature provided by hardware

- Admin/root user state is managed in software